## **DrivExpress User's Manual**

- Advanced PCI Express Verification Tool -

Doc No: MOUTBD0665 Revision: A Date: Nov. 16. 2012

macnica

# DrivExpress

#### ©2012 MACNICA AMERICAS, Inc. MACNICA, Inc. All rights reserved.

- 1. This document contains information that is proprietary to MACNICA AMERICAS, Inc. and MACNICA, Inc. You may reprint or reproduce this document in whole or in part for internal business purposes only, provided that this entire notice is preserved in all copies. In reprinting or reproducing any part of this document, the recipient agrees that every reasonable effort shall be made to prevent the unauthorized use and distribution of the proprietary information.

- 2. All information contained in this document is intended to ensure proper understanding of the product callded DrivExpress<sup>™</sup>. MACNICA AMERICAS, Inc. and MACNICA, Inc. reserve the right to make changes in contents contained in this document without prior notice, and you should, in all cases, consult MACNICA AMERICAS, Inc. or MACNICA, Inc. to determine whether any changes have been made.

- 3. MACNICA AMERICAS, Inc. and MACNICA, Inc. shall make no warranty or no liability with regard to any representation or other affirmation of fact contained in this document.

- 4. To the extent permitted by applicable law, this document is being provided on an "as-is" basis without any warranties of any kind respecting this document materials, either express or implied, including but not limited to any warranty of design, merchantability, fitness for a particular purpose, or non-infringement.

- 5. In no event shall MACNICA AMERICAS, Inc. and MACNICA, Inc. be liable for any damage whatsoever arising out of the use of or inability to use this document, even if MACNICA AMERICAS, Inc. and MACNICA, Inc. have been advised of the possibility of such damages.

- 6. The terms and conditions governing the sale and licensing of the product are set forth in written agreements between MACNICA AMERICAS, Inc. or MACNICA, Inc. and its customers.

MACNICA AMERICAS, Inc. 380 Stevens Ave., Suite 206 Solana Beach, CA 92075 Website: http://www.macnica-na.com

MACNICA, Inc. 1-6-3 Shin-Yokohama, Kouhoku-ku, Yokohama, 222-8561 Website: http://mssp.macnica.co.jp

# CONTENTS

| 1 | <b>Wha</b><br>1.1 | t is DrivExpress       1         Features       3                |

|---|-------------------|------------------------------------------------------------------|

|   | 1.2               | Simulation Environment                                           |

|   | 1.3               | References                                                       |

| 2 | Tuto              | rial 7                                                           |

|   | 2.1               | Making the DUT                                                   |

|   | 2.2               | Making The Test Environment                                      |

|   | 2.3               | Writing A Test Script (Part 1)                                   |

|   |                   | 2.3.1 Creating The Simulation Model                              |

|   |                   | 2.3.2       Access to Configuration Registers       15           |

|   | 2.4               | Running The Verilog Simulation   17                              |

|   | 2.5               | Writing A Test Script (Part 2)                                   |

|   |                   | 2.5.1 MSI Interrupt Handling                                     |

|   |                   | 2.5.2       Preparation for the DMA transfer       20            |

|   |                   | 2.5.3       Starting the DMA transfer and waiting for completion |

|   |                   | 2.5.4     Non-Posted and Posted     22                           |

|   | 2.6               | About the automatic TCL script                                   |

|   |                   |                                                                  |

| 3 | Best              | Practices 25                                                     |

|   | 3.1               | Python Classes                                                   |

|   | 3.2               | Command Queue and Command Type                                   |

|   |                   | 3.2.1 Simulation Cost                                            |

|   |                   | 3.2.2 Command Execution Order                                    |

|   | 3.3               | Split of Test Script Files                                       |

|   |                   | 3.3.1 File Expansion                                             |

|   |                   | 3.3.2 File Execution                                             |

|   | 3.4               | Delayed Execution                                                |

|   |                   | 3.4.1 Delayed Parameter Setting 35                               |

|   |                   | 3.4.2 Delayed Function Execution                                 |

|   | 3.5               | PCI Express Commands and TLPs                                    |

|   |                   | 3.5.1 Split by Max Payload Size                                  |

|   |                   | 3.5.2 Relationship between Memory Read TLP and Tag Field         |

|   |                   | 3.5.3 Passing Memory Write Command                               |

|   | 3.6               | DrivExress TLP FIFO                                              |

|   |                   | 3.6.1 Egress TLP FIFO                                            |

|   |                   | 3.6.2 Ingress TLP FIFO                                           |

|   |                   | 3.6.3 Non-Posted Request FIFO                                    |

|   | 3.7               | Verilog Task and Shell Module                                    |

|   | 3.8          | 3.7.1<br>3.7.2<br>Connect<br>3.8.1<br>3.8.2                                                                                                                                                                                                                                                                                            | PCI Express PIPE Interface Model                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                     | 51<br>52<br>55<br>55<br>56                                                                                      |

|---|--------------|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-----------------------------------------------------------------------------------------------------------------|

| 4 | 4.17         | Issues m<br>Changes<br>Controls<br>Changes<br>Issues m<br>Sets Rea<br>Transmi<br>Expands<br>Adds Cl<br>Changes<br>Specifie<br>Waits un<br>Dumps t<br>Loads th<br>Waits fo                                                                                                                                                              | nemory read/write TLP with 64-bit address                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                            | <b>59</b><br>60<br>61<br>62<br>63<br>64<br>65<br>66<br>70<br>72<br>73<br>74<br>75<br>78<br>78<br>80<br>82<br>84 |

| 5 | Class<br>5.1 | <b>Referen</b><br>PCI Exp<br>5.1.1<br>5.1.2<br>5.1.3<br>5.1.4<br>5.1.5<br>5.1.6<br>5.1.7<br>5.1.8<br>5.1.9<br>5.1.10<br>5.1.11<br>5.1.12<br>5.1.13<br>5.1.14<br>5.1.12<br>5.1.13<br>5.1.14<br>5.1.15<br>5.1.16<br>5.1.17<br>5.1.16<br>5.1.17<br>5.1.18<br>5.1.19<br>5.1.20<br>5.1.21<br>5.1.22<br>5.1.23<br>5.1.24<br>5.1.25<br>5.1.26 | press Root Complex class       Ink event detection command       Ink         Configuration space 8-bit read command       Ink         Configuration space 16-bit read command       Ink         Configuration space 32-bit read command       Ink         Configuration space 8-bit write command       Ink         Configuration space 8-bit write command       Ink         Configuration space 16-bit write command       Ink         Configuration space 32-bit write command       Ink         Configuration space 32-bit write command       Ink         Memory space 8-bit read command       Ink         Memory space 8-bit read command       Ink         Memory space 16-bit read command       Ink         Memory space 16-bit read command       Ink         Memory space 8-bit write command       Ink         Memory space 32-bit write command       Ink         Memory space 32-bit write command       Ink         Memory space 32-bit write comm | 03<br>04<br>05<br>06<br>07<br>08<br>09<br>10<br>11<br>12<br>13<br>14<br>15<br>16                                |

|     | 5.1.27  | Ingress TLP raw data print enabling parameter          |

|-----|---------|--------------------------------------------------------|

|     | 5.1.28  | Egress DLLP raw data print enabling parameter          |

|     | 5.1.29  | Egress TLP raw data print enabling parameter           |

|     | 5.1.30  | Framer/Striper behavior print enabling parameter 121   |

|     | 5.1.31  | De-Striper/De-Framer behavior print enabling parameter |

|     | 5.1.32  | LTSSM report enabling parameter                        |

|     | 5.1.33  | InitFC report enabling parameter                       |

|     | 5.1.34  | Configuration read TLP report enabling parameter       |

|     | 5.1.35  | Configuration write TLP report enabling parameter 126  |

|     | 5.1.36  | Memory read TLP report enabling parameter 127          |

|     | 5.1.37  | Memory write TLP report enabling parameter             |

|     | 5.1.38  | Completion with data TLP report enabling parameter     |

|     | 5.1.39  | Completion without data TLP report enabling parameter  |

|     | 5.1.40  | Requester ID setting parameter                         |

|     | 5.1.41  | Bus number setting parameter                           |

|     | 5.1.42  | Device number setting parameter                        |

|     | 5.1.43  | Function number setting parameter                      |

|     | 5.1.44  | Max Payload Size setting parameter                     |

|     | 5.1.45  | Egress TLP FIFO size setting parameter                 |

|     | 5.1.46  | Ingress TLP FIFO size setting parameter                |

|     | 5.1.47  | Egress TLP FIFO pop timing delay parameter             |

|     | 5.1.48  | Ingress TLP FIFO pop timing delay parameter            |

|     | 5.1.49  | Non-posted TLP request time-out parameter              |

| 5.2 | Host M  | emory class                                            |

|     | 5.2.1   | 8-bit read command                                     |

|     | 5.2.2   | 16-bit read command                                    |

|     | 5.2.3   | 32-bit read command                                    |

|     | 5.2.4   | Read command                                           |

|     | 5.2.5   | 8-bit write command                                    |

|     | 5.2.6   | 16-bit write command                                   |

|     | 5.2.7   | 32-bit write command                                   |

|     | 5.2.8   | Write command                                          |

|     | 5.2.9   | Immediate 8-bit read command                           |

|     | 5.2.10  | Immediate 16-bit read command                          |

|     | 5.2.11  | Immediate 32-bit read command                          |

|     | 5.2.12  | Immediate read command                                 |

|     | 5.2.13  | Immediate 8-bit write command                          |

|     | 5.2.14  | Immediate 16-bit write command 157                     |

|     | 5.2.15  | Immediate 32-bit write command                         |

|     | 5.2.16  | Immediate write command                                |

|     | 5.2.17  | Memory access event wait command                       |

|     | 5.2.18  | Memory access event callback command 162               |

|     | 5.2.19  | Event enabling command                                 |

|     | 5.2.20  | Event disabling command                                |

|     | 5.2.21  | Memory dump command                                    |

|     | 5.2.22  | Read memory file command 168                           |

|     | 5.2.23  | Write memory file command                              |

|     | 5.2.24  | Immediate memory dump command                          |

|     | 5.2.25  | Immediate read memory file command                     |

|     | 5.2.26  | Immediate write memory file command 172                |

| 5.3 | Simulat | ion Control class                                      |

|     | 5.3.1   | Wait command                                           |

|     | 5.3.2   | Reset command                                          |

|     | 5.3.3   | Simulation stop command 176                            |

|     | 5.3.4    | Simulation quit command                                      |

|-----|----------|--------------------------------------------------------------|

|     | 5.3.5    | Simulation statistics print command 178                      |

|     | 5.3.6    | Print message command                                        |

|     | 5.3.7    | Immediate print message command                              |

|     | 5.3.8    | Run code string command                                      |

|     | 5.3.9    | Run script file command                                      |

|     | 5.3.10   | Expand script file command                                   |

|     | 5.3.11   | Log file generation command                                  |

|     | 5.3.12   | DrivExpress log style for message command enabling parameter |

|     | 5.3.13   | License file setting parameter                               |

|     | 5.3.14   | Command execution interval setting parameter 187             |

|     | 5.3.15   | Random seed value setting parameter                          |

|     | 5.3.16   | Simulation time get parameter                                |

| 5.4 | Pre-defi | ned Macro                                                    |

|     | 5.4.1    | Link State Definition Macro 191                              |

|     | 5.4.2    | Memory Access Definition Macro 192                           |

|     | 5.4.3    | Configuration Space Register Address Definition Macro 193    |

|     | 5.4.4    | Configuration Space Register Data Definition Macro 195       |

|     |          |                                                              |

Index

197

CHAPTER

# WHAT IS DRIVEXPRESS

DrivExpress<sup>™</sup> provides a fast and easy-to-use verification environment for PCI Express® Endpoint FPGA designs that use ALTERA® PCI Express IP. By using DrivExpress with ModelSim® Verilog simulators <sup>1</sup>, system level test scripts can be developed easily.

Because the PCI Express Root Complex model included in DrivExpress has been written in the C++ language, simulation time is much shorter compared with traditional verification environments consisting of Verilog bus functional models.

Users write test scripts in the high level scripting language Python $\mathbb{R}^2$ , therefore, test script development work using DrivExpress is just like developing actual device driver software. It provides a good environment for hardware-software co-design.

<sup>&</sup>lt;sup>1</sup> Supporting ModelSim ASE/AE/PE/DE/SE or Questa

<sup>&</sup>lt;sup>2</sup> "Python" is a registered trademark of the Python Software Foundation

Design Verification by HW engineers

Runs simulation by DrivExpress for FPGA design integrated with ALTERA PCI Express IP

Writing Script by SW engineers

Writes the same sequence of generating bug in Python and provides it to HW enginerrs Driver Development by SW engineers

Easy to develop software by Python script used in the simulation (It can be serve as Design Spec)

System Level Verification for design on the board by HW and SW engineers

Detection of BUG !

Figure 1.1: DrivExpress Verification Flow

## 1.1 Features

- PCI Express Gen1, Gen2, Gen3<sup>3</sup> support

- x1 x8 Multi-Lane support

- Fast Verilog simulation due to C++ model

- Simple and easy-to-use Python classes

- PCI Express Root Complex Class

- Host Memory Class

- Simulation Control Class

- Flexible Event Control

- PCI Express Link Event

- Memory Access Event (like MSI Events)

- PCI Express Transaction Log Control

- DPI Connection to Verilog Design

<sup>&</sup>lt;sup>3</sup> Expected release in Q1, 2013

## **1.2 Simulation Environment**

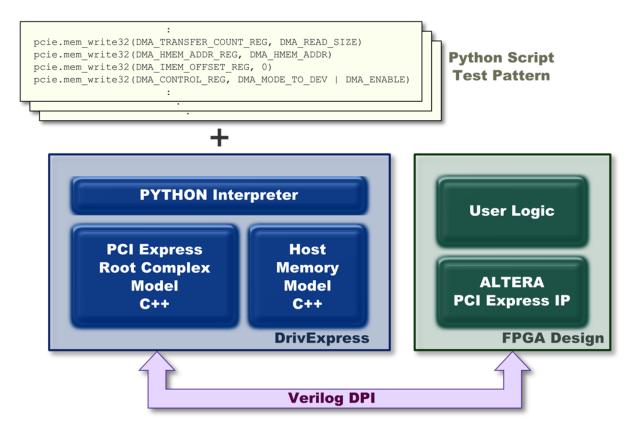

DrivExpress is provided as shared library (Windows dll file or Linux so file). This library is loaded into the Verilog simulator along with the DUT  $^4$  – a PCI Express Endpoint FPGA design that uses the ALTERA PCI Express IP.

Because DrivExpress has a built-in Python interpreter, users write test scripts for the DUT in Python. At the beginning of Verilog simulation, the Python script written by user is read and the commands in the script are executed as part of the Verilog simulation process. All Python classes provided by DrivExpress have been written in the C++ language and the corresponding C++ code is called when the Python interpreter executes the commands or parameters supported by those classes. The C++ code, in turn, controls the DUT through Verilog DPI interface.

All commands and parameters of the Python classes of DrivExpress have been abstracted away to a high level, mirroring software development, such that users can understand the code instinctively. Anybody can quickly write code to access to the PCI configuration space or PCI memory space (including the user's original registers mapped into that space) even without special knowledge of Python. In addition to this, by using the memory event detect function provided by DrivExpress, things like MSI event handling can be written into the Python scripts in a similar fashion to writing actual interrupt handlers in software.

#### Python Script Example:

```

pcie = PcieRootComplex() # Create instance of PCIe Root Complex

# Access to congiguration space registers

pcie.cfg_read16(VENDOR_ID, 0x1172)

pcie.cfg_read16(DEVICE_ID, 0x0004)

pcie.cfg_write32(BAR0, BASE_ADDR_MEM)

pcie.cfg_write32(BAR2, BASE_ADDR_REG)

pcie.cfg_write16(COMMAND, PERR_RESPONSE | BUS_MASTER_ENABLE | MEM_SPACE_ENABLE)

# Access to Memory Mapped DMA regsiters

pcie.mem_write32(DMAR_CNTL_REG, DMA_DESC_COUNT)

pcie.mem_write32(DMAR_DESC_ADDR_HI_REG, DMAR_DESC_ADDR >> 32)

pcie.mem_write32(DMAR_DESC_ADDR_LO_REG, DMAR_DESC_ADDR & 0xFFFFFFFF)

```

<sup>&</sup>lt;sup>4</sup> Design Under Test

Figure 1.2: DrivExpress Verification Environment Image

## **1.3 References**

DrivExpress is a verification tool for PCI Express Endpoint FPGA designs integrated with ALTERA PCI Express IP. It is used with the Mentor family of Verilog simulators. Users should ideally have a working knowledge of the simulator as well as the PCI Express specification and ALTERA PCI Express IP. For issues relating to the Verilog simulator, please refer to the manual accompanying that product. For PCI Express-related questions, the following documents may be useful for reference.

- PCI Express® Base Specification Revision 2.1

- PHY Interface for the PCI Express™ (PIPE) Architecture Version 1.00

- ALTERA® IP Compiler for PCI Express User Guide

For Python-related issues, online documents provided and maintained by the Python Software Foundation may be helpful.

• http://docs.python.org/

## CHAPTER

# TUTORIAL

In this chapter, we create a design (DUT) that integrates a DMA controller with the ALTERA PCI Express IP. After this we provide step-by-step instructions on how to write a test script for the design using DrivExpress Python commands, and then describe how to run the Verilog simulation using ModelSim.

Note that this design represents a fairly complex system which exercises many of the DrivExpress features. Once a user has mastered the steps required to build and operate the tutorial design, almost any other DrivExpress project can be built easily.

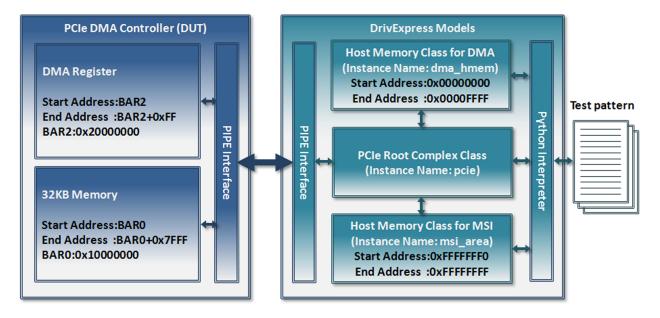

The following diagram show the simulation model environment used in this tutorial.

Figure 2.1: Simulation model environment used in this tutorial

#### PCI Express Chaining DMA Controller (DUT)

The DUT in this tutorial is a DMA controller integrated with the ALTERA PCI Express IP. It consists of 32KB of internal memory and DMA registers. These are mapped to PCI memory space, which is 0x1000000-0x10007FFF and 0x20000000-0x200000FF respectively. This is controlled by DrivExpress.

#### PCI Express Root Complex Model

The PCI Express Root Complex controls the DUT. It is connected to the DUT through the PIPE interface <sup>*a*</sup> and performs PCI configuration accesses and memory accesses to the DUT.

<sup>*a*</sup> PHY Interface for the PCI Express<sup>TM</sup> Architecture

#### Main Memory for DMA Transfers (Host Memory Class for DMA)

This is a buffer on host memory. It is mapped to PCI memory space 0x0000000-0x0000FFFF (64KB) as a part of host memory and used as the source or destination for the DMA transfers to/from the DUT.

#### Main Memory for Interrupt Messages (Host Memory Class for MSI)

This is a memory area for receiving Message Signal Interrupts. It is mapped to PCI memory space 0xFFFFFF0-0xFFFFFFF (16 bytes) as part of host memory. DrivExpress controls DUT and lets it issue MSI's to this area.

#### Note:

- 1. Linux notation for the directory path or command is described in this manual. Please change to the corresponding commands if using Windows.

- 2. Install directory for DrivExpress is expressed as \$DRIVEXPRESS\_ROOTDIR.

- 3. Install directory for ALTERA Quartus® II is expressed as \$QUARTUS\_ROOTDIR.

- 4. All commands start with the symbol \$. In cases where a command line example is longer than effective area of the example, no \$ is shown on subsequent lines and those lines continue below. For example, the following command is used to change directory.

- \$ cd \$DRIVEXPRESS\_ROOTDIR/sample/design/gen2x4/pcie\_proj\_examples/chaining\_dma

/drivexpress\_tb

#### 5. This tutorial uses one of the sample scripts located in

\$DRIVEXPRESS\_ROOTDIR/sample/design/script directory. The file name of the script is

test\_main\_tutorial.py. In addition, a TCL script to run the Verilog simulation automatically is

located in \$DRIVEXPRESS\_ROOTDIR/sample/design/build\_run.do. The following steps run

test\_main\_tutorial.py using the build\_run.do file.

```

$ cd $DRIVEXPRESS_ROOTDIR/sample/script

$ mv test_main.py test_main_sample.py

$ mv test_main_tutorial.py test_main.py

$ cd $DRIVEXPRESS_ROOTDIR/sample/design

$ vsim < build_run.do</pre>

```

For more information about the build\_run.do file, please refer to "About the automatic TCL script".

## 2.1 Making the DUT

The first step is to make the PCI Express Chaining DMA controller DUT. This design is generated using the ALTERA Quartus II MegaWizard Plug-in Manager tool. The MegaWizard not only generates a PCI Express IP core, but also creates an example design and simple testbench (that we will replace with DrivExpress) that uses the IP core. This tutorial takes advantage of the generated example design.

Note that this step and the next is performed automatically by the build\_run.do TCL file included in the DrivExpress installation. These steps are described here so the user can get a better idea of how the DrivExpress examples are executed and as an example of how one might set up their simulation environment to include DrivExpress.

A top level IP file has been provided in the DrivExpress installation for several PCI Express configurations. The MegaWizard will open the top level file, which contains the configuration information and generate all the supporting files needed by the IP core, as well as examples used here.

To begin, in Quartus start the MegaWizard Plug-in Manager from the "Tools" menu, or execute the qmegawiz command located in the *\$QUARTUS\_ROOTDIR/bin* directory. Once the MegaWizard Plug-in Manager window is displayed, select "Edit an existing custom megafunction variation" and click the Next button.

| 🐇 MegaWizard Plug-In Manager [page 1] 🛛 🛛 🛛 |                                                                                                                                                                                                                                                                                                                                                                 |  |  |  |

|---------------------------------------------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--|--|--|

| *                                           | The MegaWizard Plug-In Manager helps you create or modify design files that contain custom variations of megafunctions.<br>Which action do you want to perform?<br>Create a new custom megafunction variation<br>Edit an existing custom megafunction variation<br>Copy an existing custom megafunction variation<br>Copyright (C) 1991-2011 Altera Corporation |  |  |  |

|                                             | Cancel < Back Next > Finish                                                                                                                                                                                                                                                                                                                                     |  |  |  |

In the next window, specify the sample MegaWizard configuration  $^1$  file provided by the DrivExpress installation. In the following example, although the PCI Express Gen2 x4 has been selected, another design, such as Gen1 x1 can be specified. After selecting the file, click the Next button.

| 🐇 MegaWiza                        | rd Plug-In Manager [page 2b]                                                                                                                                                                                       |

|-----------------------------------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

|                                   |                                                                                                                                                                                                                    |

|                                   | n megafunction variation file do you wish to edit?                                                                                                                                                                 |

| Look in: 🛅                        | ) C1/drivexpress/sample/design/gen2x4 🕑 🖸 😳 🖓 🎾 🔃 🔳                                                                                                                                                                |

| Die_pro                           | ol.v                                                                                                                                                                                                               |

|                                   |                                                                                                                                                                                                                    |

|                                   |                                                                                                                                                                                                                    |

|                                   |                                                                                                                                                                                                                    |

|                                   |                                                                                                                                                                                                                    |

|                                   |                                                                                                                                                                                                                    |

|                                   |                                                                                                                                                                                                                    |

|                                   |                                                                                                                                                                                                                    |

| File <u>n</u> ame:                | pcie_proj.v                                                                                                                                                                                                        |

| Files of type:                    | All Megafunction Files (*.tdf *.vhd *.vhl *.v)                                                                                                                                                                     |

| Show only                         | y wizard-generated files                                                                                                                                                                                           |

| 🗌 Return to                       | ) this page for another edit operation                                                                                                                                                                             |

| The current m<br>following list:. | negafunction variation is based on the megafunction shown below. If you want to use a different megafunction as the basis for your changes to this custom variation, select a different megafunction name from the |

| Megafunction                      | name: IP Compiler for PCI Express v11.1                                                                                                                                                                            |

|                                   |                                                                                                                                                                                                                    |

|                                   | Cancel <back next=""> Enish</back>                                                                                                                                                                                 |

When the IP Compiler for PCI Express window is displayed, click the Finish button, and the generation process for the design will start.

| 🔨 MegaWizard Plug-In Manage                                                                                                                                                                                                                         | r – IP Compiler for    | PCI Express           |                       |                      |  |

|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|------------------------|-----------------------|-----------------------|----------------------|--|

| IP Compilei                                                                                                                                                                                                                                         | r for PCI Exp          | press                 |                       | About Documentation  |  |

| 1 Parameter 2 EDA 3 Summa<br>Settings                                                                                                                                                                                                               |                        | "                     |                       |                      |  |

| System Settings > PCI Registers                                                                                                                                                                                                                     | 🔪 Capabilities 🔪 Bu    | uffer Setup > Power M | anagement >           |                      |  |

| PCIe Core Type                                                                                                                                                                                                                                      |                        |                       |                       |                      |  |

| Hard IP for PCI Express     Soft IP for PCI Express     Hard IP for PCI Express     The hard IP uses embedded dedicated logic to     implement the PCI Express protocol stack, including physical layer,     data link layer and transaction layer. |                        |                       |                       | -                    |  |

|                                                                                                                                                                                                                                                     | s                      |                       |                       |                      |  |

| PHY type: Stratix IV GX                                                                                                                                                                                                                             | PHY interface:         | Serial 🗸              | Configure             | transceiver block    |  |

| Lanes: x4                                                                                                                                                                                                                                           | Xcvr ref_clk: 1        | 00 MHz                | Application interface | Avalon-ST 64-bit     |  |

| Port type: Native Endpoint                                                                                                                                                                                                                          | PCI Express version: 2 | 2.0 🗸                 | Application clock:    | 250 MHz 🗸            |  |

| Max rate: Gen2 (5.0 Gbps)                                                                                                                                                                                                                           | Test out width: 6      | i4 bits 🔽             | HIP reconfig:         | Disable              |  |

|                                                                                                                                                                                                                                                     |                        |                       |                       |                      |  |

| <ol> <li>Info: Native Endpoint implementation requires MSI message 64-bit address capability.</li> <li>Info: Native Endpoint implementation doesn't support I/O or 32-bit Prefetchable memory BAR types.</li> </ol>                                 |                        |                       |                       |                      |  |

|                                                                                                                                                                                                                                                     |                        |                       | Cancel                | < Back Next > Einish |  |

1 \$DRIVEXPRESS\_ROOTDIR/sample/design/gen2x4/pcie\_proj.v

Click the Exit button once generation has completed.

| 📉 Generation – IP Compiler for PCI Express 11.1                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                         |      |

|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|------|

| <ul> <li>Info: pcie_proj: generating HDL</li> <li>Info: pcie_proj: Variation name : pcie_proj</li> <li>Info: pcie_proj: Variation language : Verilog HDL</li> <li>Info: pcie_proj: Output directory : C:\drivexpress\sample\design\gen2x4</li> <li>Info: pcie_proj: Generating HDL</li> <li>Info: pcie_proj: Generating metlist using chosen parameters</li> <li>Info: pcie_proj: Generating Verilog HDL IP functional simulation model</li> <li>Info: pcie_proj: Updating user's project directory</li> <li>Info: pcie_proj: HDL generated</li> <li>Info: pcie_proj: Generation successful.</li> </ul> |      |

| Generation Successful Cancel                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                            | Exit |

The pcie\_proj\_examples/chaining\_dma directory should have been generated in the the directory you selected (for example, in \$DRIVEXPRESS\_ROOTDIR/sample/design/gen2x4/). This /chaining\_dma directory contains the files used as the DUT in this tutorial. It contains an example design using the PCIe IP core configuration generated by the MegaWizard. The ALTERA MegaWizard also creates a Verilog-based testbench for the design that will be replaced with DrivExpress.

Please refer to "Chapter 15: Testbench and Design Example" of ALTERA® IP Compiler for PCI Express User Guide for more information about the Chaining DMA controller used as the DUT in this tutorial.

## 2.2 Making The Test Environment

The next task is to compile the DUT design and testbench file so the Verilog simulation can be run.

Create the simulation execution directory drivexpress\_tb in the DUT's pcie\_proj\_examples/chaining\_dma directory and copy the following files to there.

- All Verilog files in pcie\_proj\_examples/chaining\_dma/testbench directory

- The DrivExpress testbench Verilog file

- The Verilog file which instantiates the DrivExpress Verilog shell module

- The DrivExpress license file

#### Note:

1. The testbench Verilog file for the simulation drvex\_tb.v should be selected suitably based on the number of PCI Express lanes on the DUT.

For example, select <code>\$DRIVEXPRESS\_ROOTDIR/sample/design/x4/drvex\_tb.v</code> for a DUT that has a x4 lane configuration.

- 2. The Verilog shell file is located in *\$DRIVEXPRESS\_ROOTDIR/lib* directory.

- 3. The DrivExpress license file should be obtained separately because it is not installed automatically. If you don't have a license file, please sign up to receive it at DrivExpress License Request Form. In this tutorial, it is supposed that the license file is in \$DRIVEXPRESS\_ROOTDIR directory.

The command example for Gen2 x4 DUT design is shown below.

```

$ cd $DRIVEXPRESS_ROOTDIR/sample/design/gen2x4/pcie_proj_examples/chaining_dma

```

\$ mkdir drivexpress\_tb

- \$ cp ./testbench/\*.v drivexpress\_tb

- \$ cp \$DRIVEXPRESS\_ROOTDIR/sample/design/x4/drvex\_tb.v drivexpress\_tb

- \$ cp \$DRIVEXPRESS\_ROOTDIR/lib/pcie\_pipe\_dpi\_shell.v drivexpress\_tb

- \$ cp \$DRIVEXPRESS\_ROOTDIR/drivexpress\_lic\_enc.bin drivexpress\_tb

If your Verilog simulator is not an ALTERA edition (ModelSim-ALTERA Edition or ModelSim-ALTERA Starter Edition), it is necessary to compile libraries for the ALTERA device. If that is the case, execute the following commands. Users, using an ALTERA edition simulator can skip this step.

```

$ cd $DRIVEXPRESS_ROOTDIR/sample/design/gen2x4/pcie_proj_examples/chaining_dma

/drivexpress_tb

$ vlib altera_mf_ver

$ vlib lpm_ver

$ vlib lpm_ver

$ vlib stratixiv_hssi_ver

$ vlib stratixiv_pcie_hip_ver

$ vlib stratixiv_pcie_hip_ver

$ vlog $QUARTUS_ROOTDIR/eda/sim_lib/altera_mf.v -work altera_mf_ver

$ vlog $QUARTUS_ROOTDIR/eda/sim_lib/sgate.v -work lpm_ver

$ vlog $QUARTUS_ROOTDIR/eda/sim_lib/stratixiv_hssi_atoms.v -work stratixiv_hssi_ver

$ vlog $QUARTUS_ROOTDIR/eda/sim_lib/stratixiv_pcie_hip_atoms.v -work

$ vlog $ vlo

```

Compile the Verilog files for DrivExpress and DUT design as follows.

```

$ cd $DRIVEXPRESS_ROOTDIR/sample/design/gen2x4/pcie_proj_examples/chaining_dma

/drivexpress_tb

$ vlib work

$ vlog -sv -work work ./drvex_tb.v

$ vlog -sv -work work ./pcie_pipe_dpi_shell.v

$ vlog -sv -work work

+incdir+../../common/testbench/+../../common/incremental_compile_module+..

-f ../testbench/sim_filelist

```

The final vlog command compiles a list of files required by the DUT. This list is kept in a file that was created by the MegaWizard when it generated the rest of the design example being used at the DUT.

Now the environment is ready for the simulation to be run.

## 2.3 Writing A Test Script (Part 1)

Before writing test script, it is important to get an understanding of when that script is read and when the commands are executed during the Verilog simulation process.

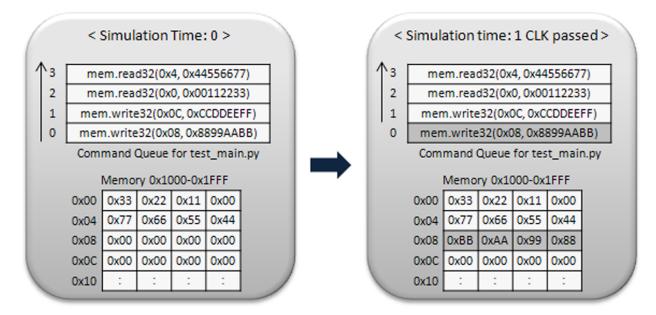

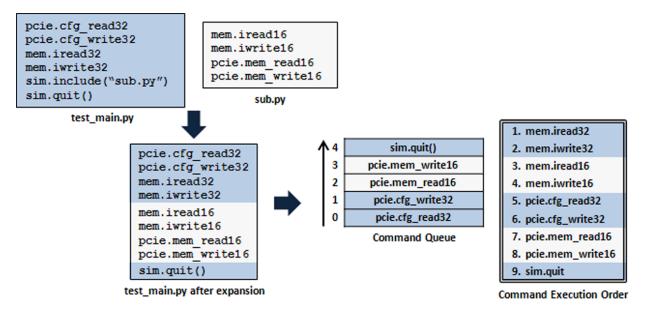

At the beginning of the Verilog simulation, the test\_main.py file located in the simulation running directory is loaded. The built-in Python interpreter interprets the contents of the test\_main.py file and pushes some commands provided by DrivExpress to the internal command queue. After that, those commands are popped from the queue and executed as simulation time advances. In practice, a Verilog clock signal is connected to the queue and each command in the queue is retrieved and executed with every command clock tick.

DrivExpress provides three Python classes which are the Root Complex class, the Host Memory class, and the Simulation control class. By using these three classes, the DUT can be controlled.

## 2.3.1 Creating The Simulation Model

Create a new file called test\_main.py and write the following code in it.

Line Numbers 1-8 (test\_main.py)

```

from dxpress import *

from a sime of the simulation control instance

from a sime of the dynamic of the simulation control instance

from a sime of the dynamic of the dyn

```

First line is required by Python to load the DrivExpress functions. Please always include it as-is.

At line number 3, the first instance of the Simulation Control class is created by and named sim. Because users can create only one instance of the Simulation Control class, it is usually created at the top of the test\_main.py file.

From line numbers 4 to 6, simulation models used in this tutorial are created. At line number 4, the Root Complex model is created and named pcie. At line number 5, a Host Memory model for the DMA buffer is created and located at memory area 0x00000000-0x0000FFFF. It is named dma\_hmem. At line number 6, a Host Memory model for the MSI buffer is created and located at memory area 0xFFFFFFF0-0xFFFFFFFF. It is named dma\_hmem.

At this point, all the simulation models explained at the beginning of this chapter have been created.

At line number 8, the log file in which DrivExpress messages are written is specified.

Each class of DrivExpress provides commands and parameters. In the normal object-oriented convention, when executing or setting these, the command name or parameter name is put after the class instance name separated by a period. So, in this case, line number 8 is executing the  $log_file()$  command of the Simulation Control class instance sim.

Note:

1. All commands and parameters bond with a class instance. For example, the following two commands are completely different although using same command write8(0, 0xFF).

dma\_hmem.write8(0, 0xFF) # Write 8bit data 0xFF to offset address 0 of dma\_hmem

msi\_area.write8(0, 0xFF) # Write 8bit data 0xFF to offset address 0 of msi\_area

It means that first write8() command is writing 0xFF data to offset address 0 of dma\_hmem (0x0000000-0x0000FFFF) and second write8() command is writing 0xFF data to offset address 0 of msi\_area (0xFFFFFF0-0xFFFFFFF). Those are corresponding with writing to absolute address 0x00000000 and 0xFFFFFFF0 respectively.

2. With respect to the terms "command" and "parameter", although these are normally called "method" and "attribute" respectively from the point of view of the Python language, the terms "command" and "parameter" are used on purpose because it is easier to understand for those users of DrivExpress not familiar with Python.

## 2.3.2 Access to Configuration Registers

The next step is setting the PCI configuration registers on the DUT. Please add the following code.

#### Line Numbers 10-31 (test\_main.py)

```

pcie.link_event_wait(LINK_READY) # Waits until PCIe Link is ready

1

2

# Check VENDOR and DEVICE ID

3

pcie.cfg_read16(VENDOR_ID, 0x1172)

4

pcie.cfg_read16(DEVICE_ID, 0x0004)

5

6

# Set BAR0 and BAR2 configration register of DUT

7

pcie.cfg_write32(BAR2, 0x2000000)

8

pcie.completion_wait() # Wait for completion for first config write TLP

9

pcie.cfg_write32(BAR0, 0x1000000)

10

11

# MSI settings for DUT

12

pcie.cfg_write32(MSI_MSG_ADDRESS, 0xFFFFFF0)

13

pcie.cfg_write16(MSI_MSG_DATA,

0x55AA)

14

pcie.cfg_write16(MSI_MSG_CONTROL, MSI_ENABLE)

15

16

# Enable Bus Master function and Memory space

17

pcie.cfg_write16(COMMAND, (PERR_RESPONSE

18

BUS_MASTER_ENABLE |

19

MEM_SPACE_ENABLE))

20

21

pcie.completion_wait() # Wait for completion for configration access

22

```

At line number 1 (corresponding to line number 10 of test\_main.py) of above code block, the Root Complex pcie is waiting until link is ready.

At line number 4 and 5, the Root Complex is reading data from the Vendor ID and Device ID configuration registers. In this case, 0x1172 and 0x0004 are passed to the read16() command respectively. Those values are the expected results from the read, and an error message is displayed during Verilog simulation if actual value returned is different from the expected value.

At line number 8, DMA registers of the DUT are mapped to PCI memory space by writing memory address to the Base Address Register 2 configuration register.

At line number 9, the Root Complex waits for the completion of first PCI configuration write cycle. Because the completion ID of DUT will change during the first configuration write cycle, waiting for the completion TLP with new completion ID is necessary.

At line number 10, 32KB of internal memory of DUT is mapped to PCI memory space 0x10000000-0x10007FFF by writing to the Base Address Register 0 configuration register.

From line number 13 to 15, address and data of MSI are set. Actually, MSI registers are set so that the DUT will write the value 0x55AA to memory address 0xFFFFFF0.

From line number 18 to 20, the command register is set so that bus master and memory address decode functions of DUT are enabled.

At line number 22, Root Complex is waiting for all configuration write commands (after line number 10) to complete. At this point the minimum settings for operation of this DUT have been completed and we can access the DUT's DMA registers and 32KB internal memory.

## 2.4 Running The Verilog Simulation

Although we just set some configuration registers in the DUT, let's run the Verilog simulation for the code so far.

Put the following code at the bottom of the file test\_main.py and save it. After that, copy the test\_main.py file to the simulation directory drivexpress\_tb.

#### Line Numbers 33-34 (test\_main.py)

```

sim.stats() # Display simulation result stats

sim.quit() # Finish simulation

```

The stats () command displays DrivExpress message statistics from the simulation. The quit () command instructs the simulator to end the simulation.

To run the simulation, execute the following command under the drivexpress\_tb directory. The command linebased method is used here to run. Alternately, the simulation can be run by typing the same command into the command window of the GUI. Please refer to the accompanying manual to your simulator for details.

#### Linux OS

```

$ vsim -sv_lib $DRIVEXPRESS_ROOTDIR/lib/libdxpress -L altera_mf_ver -L lpm_ver

-L sgate_ver -L stratixiv_hssi_ver -L stratixiv_pcie_hip_ver -noimmedca -t ps

-novopt drvex_tb -do "run -all"

```

#### Windows OS

```

$ vsim -sv_lib $DRIVEXPRESS_ROOTDIR/lib/dxpress10 -L altera_mf_ver -L lpm_ver

-L sgate_ver -L stratixiv_hssi_ver -L stratixiv_pcie_hip_ver -noimmedca -t ps

-novopt drvex_tb -do "run -all"

```

If you can run the simulation, each command will be executed and the corresponding DrivExpress message will appear. Finally, the simulation result will be displayed by the stats() command. Also all DrivExpress messages will be written to the drivexpress.log file.

Run the simulation again after changing the expected value for Vendor ID register from 0x1172 to 0x1173. Because the actual read data is 0x1172, the following error message will be displayed.

DrivExpress !ERR from PCIe TL > Time 16438.000000: Completion for Config Read TLP, Address:000, Expected:1173, Mask:FFFF, Actual:1172

Hopefully this gives you some understanding about how to verify a DUT by using DrivEpxress. In the next section, we will set up and use the DMA controller.

## 2.5 Writing A Test Script (Part 2)

In this section, we will write the code for accessing the DUT's internal memory and DMA registers. Please delete the stats() and quit() commands added in the previous section.

It is convenient when writing a script to define certain address and bit location for the DMA registers. Please add the following code. Because we set 0x20000000 as the base address of the DMA registers in section titled "Writing A Test Script (Part 1)", each register is defined based on this address.

#### Line Number 33-57 (test\_main.py)

```

_____

1

# Chaining DMA Controller Definition

2

#_____

3

BASE_ADDR_REG = 0x20000000 # Base address of DMA registers

DMAW_CNTL_REG = BASE_ADDR_REG + 0x00

4

5

DMAW_DESC_ADDR_HI_REG = BASE_ADDR_REG + 0 \times 04

6

DMAW_DESC_ADDR_LO_REG = BASE_ADDR_REG + 0 \times 08

7

DMAW_RCLAST_INDEX_REG = BASE_ADDR_REG + 0 \times 0 C

8

= BASE_ADDR_REG + 0x10

DMAR CNTL REG

9

DMAR_DESC_ADDR_HI_REG = BASE_ADDR_REG + 0x14

10

DMAR_DESC_ADDR_LO_REG = BASE_ADDR_REG + 0x18

11

DMAR_RCLAST_INDEX_REG = BASE_ADDR_REG + 0x1C

12

DMAW\_STATUS\_HI\_REG = BASE\_ADDR\_REG + 0x20

13

DMAW_STATUS_LO_REG = BASE_ADDR_REG + 0x24

DMAR_STATUS_HI_REG = BASE_ADDR_REG + 0x28

14

15

DMAR\_STATUS\_LO\_REG = BASE\_ADDR\_REG + 0x2C

16

DMA_ERROR_REG

= BASE_ADDR_REG + 0x30

17

18

# DMA Control Register bit value

19

MSI\_ENA = 0 \times 00020000

20

EPLAST\_ENA = 0 \times 00040000

21

22

# DMA Descriptor

23

DMA_DESC_MSI_ENA

= 0 \times 00010000

24

DMA\_DESC\_EPLAST\_ENA = 0 \times 00020000

25

```

## 2.5.1 MSI Interrupt Handling

Before starting the DMA transfer, it is necessary to define and register two functions: the MSI checker function and the MSI handler function. The MSI handler function is called asynchronously from within DrivExpress when an MSI event occurs, so this kind of function is called an event callback function or callback function.

Please add the following code.

Line Numbers 59-79 (test\_main.py)

```

#____

1

# DMA Interrupt Handler

2

#_____

3

# DMA Event Detector

4

def dma_event(time, rw, addr, data):

5

if (msi_area.iread16(0) == 0x55AA): return True

6

else:

return False

8

# DMA Interrupt Handler

9

def dma_handler():

10

11

"DMA INTERRUPT"

12

13

# disable event not to call by future MSI event

14

msi_area.disable_event(ev_dma)

15

msi_area.iwrite16(0, 0x0000) # clear MSI message

16

# clear DMA control regsiter

17

pcie.mem_write32(DMAW_CNTL_REG, 0x0000FFFF)

18

19

# Register DMA Interupt Handler (not enabled yet)

20

ev_dma = msi_area.event_callback(dma_event, dma_handler)

21

```

At line number 21 (corresponding to line number 79 of test\_main.py file) of the above code block, the MSI checker and handler functions are registered. Please note that the event\_callback() command is bonded to the msi\_area. The registered event check function dma\_event() is only called for access to 0xFFFFFF0-0xFFFFFFF because of this bonding with msi\_area. Each time an event occurs in this memory area, the event check function runs to determine if the registered event has occurred. In this case if an MSI event has occurred, the event check function returns True, thus the callback function dma\_handler() is called from within DrivExpress.

Event ID is returned by executing the event\_callback() command. By using this event ID, users can disable the corresponding event\_callback() until a certain point in the code or conversely, enable it from a certain point. By default, event\_callback() is disabled, so the event check function is never called even if an access to the msi\_area occurs. In the next code block, the event\_callback() command is enabled by executing the enable\_event() command just before kicking off a DMA transfer.

From line number 5 to 7, the event check function reads 16-bit data from offset address 0 of msi\_area, which corresponds to absolute address 0xFFFFFF0, and returns True if the read value is 0x55AA. If you remember, when the DUT configuration registers were set, an MSI event was defined as a write access to address 0xFFFFFF0 with the data 0x55AA, thus the dma\_event() function is checking for an MSI interrupt.

When reading first address of msi\_area in the event check function, the iread() was used, not the read() command. A command with the leading character i is called an *immediate* command or *i*command for short. The *i*command is not pushed into the internal DrivExpress command queue of and it is executed instantly when interpreted by the built-in Python interpreter. Therefore, an *i*command does not consume Verilog simulation time. Using an *i*command for processing independent of simulation time, simulation will be much faster than the case of a queued command and also allows for checks that don't make sense as queued commands.

**Note:** As a matter of fact, any queued type command cannot be used in event check function. On the other hand, you can use both types of commands in a callback function.

From line number 10 to 18, the event callback function disables the event\_callback() command by executing disable\_event() and clears the first 16-bits of msi\_area for the next MSI detection. After that, it clears the DMA control register of DUT using the mem\_write32() command of Root Complex.

## 2.5.2 Preparation for the DMA transfer

Before starting the DMA transfer, it is necessary to do the following.

- 1. Setting the DMA registers of the DUT

- 2. Initialization of the DMA buffer

- 3. Creating the DMA descriptors

In this tutorial, we make one DMA descriptor which transfers 256 bytes of data from address 0x1000 in the dma\_hmem area to the internal memory of DUT. The DMA descriptor itself will be created in the dma\_hmem area. We assign the first 32 bytes of the dma\_hmem area to be the DMA descriptor area.

When building up descriptors, it's important to understand the perspective that we're using to formulate addresses. In this case, both the DMA buffer address in host memory (set in the DMA descriptor) and the DMA descriptor address, which will be set in the the DMA register of the DUT should use the absolute address of the PCI memory space. Because dma\_hmem is defined as 0x0000000-0x0000FFFF use the absolute address, those addresses are as follows.

- 0x00001000 Absolute address of DMA buffer on host memory

- 0x00000000 Absolute address of DMA descriptor

Line Numbers 81-97 (test\_main.py)

```

#_____

1

# DMA transfer from Host Memory to Device Memory

2

3

# Initialize 256 bytes DMA buffer (0x00001000-0x000010FF) by increment data

4

for i in range(0, 256): dma_hmem.iwrite8(0x1000 + i, i)

5

6

# Set up DMA descriptor (0x0000000-0x0000001F), first 16 bytes are reserved

7

# Transfer 256 bytes (64DW) data from host memory 0x1000 to internal device memory

8

dma_hmem.iwrite32(0x10, (DMA_DESC_EPLAST_ENA | DMA_DESC_MSI_ENA | 64))

9

dma_hmem.iwrite32(0x14, 0)# Internal device memory offset addressdma_hmem.iwrite32(0x18, 0)# Upper 32bit address of DMA buffer memory

10

# Upper 32bit address of DMA buffer memory

11

dma_hmem.iwrite32(0x1C, 0x1000) # Lower 32bit address of DMA buffer memory

12

13

# Setup DMA registers

14

pcie.mem_write32(DMAR_CNTL_REG, 1)

# DMA Descriptor Count

15

pcie.mem_write32(DMAR_DESC_ADDR_HI_REG, 0) # Upper 32bit address of DMA descriptor

16

pcie.mem_write32(DMAR_DESC_ADDR_LO_REG, 0) # Lower 32bit address of DMA descriptor

17

```

At line number 5 (corresponding to line number 85 of test\_main.py) of the above code block, 256 bytes data from offset address 0x1000 of dma\_hmem area are initialized as incremental data. We use *i*command on purpose here. This is a time-saving method to improve simulation performance. It would be possible to use the write8() command instead of iwrite8(); however, that means it takes time to retrieve each command from the queue and execute it in simulation time for all 256 commands. On the other hand, using iwrite8(), all 256 commands are executed instantly when interpreted by the built-in Python interpreter and it doesn't consume simulation time at all. Because the purpose of the design is to transfer 256 bytes of the incremental data on host memory to internal memory of DUT, it isn't meaningful to spend time on the initialization process. It is good practice to use *i*commands to reduce simulation overhead for this kind of work (setup that occurs only in the host).

From line number 9 to 12, the DMA descriptor is created in the 0x10-0x1F area of dma\_hmem. In this code, the DMA transfer count (double word), offset address of DUT internal memory, and absolute address of host memory are set. Because this process is also independent of simulation time, we use *i*command. It is necessary to keep the 0x00-0x0F area of dma\_hmem open because the DUT will use that area during DMA transfer process.

From line number 15 to 17, the DMA descriptor count and absolute address of the DMA descriptor are set in the DMA registers of DUT. Because DUT is part of the Verilog design, we want these command to be executed in simulation time (they are access that would really occur across the PCIe link to the DUT registers. For this reason, the Root Complex model does not support *i*commands.

Now, it is time to start the DMA transfer.

#### 2.5.3 Starting the DMA transfer and waiting for completion

The remaining tasks are: starting the DMA transfer and checking whether the source data was transferred to the destination address correctly after completion.

#### Line Numbers 99-122 (test\_main.py)

```

# Enable DMA interrupt event before kicking DMA transfer

1

msi_area.enable_event(ev_dma)

2

3

4

"Start DMA from Host Memory to Device Memory"

5

6

7

# Kick DMA transfer (from Host Memory to Device Memory)

8

pcie.mem_write32(DMAR_RCLAST_INDEX_REG, 0)

9

10

# Wait until DMA interrupt is processed, or timeout if 100000 clks elapsed

11

msi_area.event_wait(dma_event, 100000)

12

13

# Read and check internal device memory of chaining DMA controller

14

exp_buf = [i for i in range(256)] # Expected data is 256 bytes increment data

15

pcie.mem_read(0x10000000, 256, exp_buf) # Read 256 bytes frominternal device memory

16

pcie.completion_wait()

17

18

19

"DMA from Host Memory to Device Memory Complete"

20

21

22

sim.stats() # Display simulation result stats

23

# Finish simulation

sim.quit()

24

```

At line number 2 (corresponding to line number 100 of test\_main.py) of above code block, the event\_callback() command for msi\_area is enabled. After that, a DMA start message is output and the DMA transfer is started at line number 9.

If you have other tasks to do after starting the DMA transfer, those tasks would be written in the script. When the DMA transfer is complete, the registered callback function will be called in mid-flow. This really looks like the behavior of an interrupt routine.

In this tutorial, however, after starting the DMA transfer, we don't do anything and just wait for the DMA to complete. The code of at line number 12, which executes the event\_wait() command, allow us to wait for that. The same kind of event check function is used in the event\_wait() command here. Although the event\_wait() command is similar to event\_callback() command, there is no callback function and it just waits until the event check function returns True or a time-out occurs (which is specified as an argument representing command clocks ticks). In this code example, the registered event check function dma\_event() is called only when the DUT accesses the 0xFFFFFFF0-0xFFFFFFFF area because event\_wait() command is bonded to the msi\_area. This behavior is same as the event\_callback() command. However, when an event check function returns True, the event\_wait() command just exits whereas a registered callback function is called in the case of a event\_callback() command.

From line number 15 to 17, DrivExpress checks whether the first 256 bytes of internal memory of DUT are filled with incrementing data as a result of the DMA transfer. At line number 15, 256 bytes of expected data is generated as incrementing data in the <code>ext\_buf</code> list, and then the Root Complex reads 256 bytes data from address 0x10000000, which is the absolute address of DUT internal memory, by using mem\_read() command and checks returned data is the same as <code>ext\_buf</code>. At line number 17, the Root Complex waits for the completion of the mem\_read() command.

From line number 19 to 24, simulation will end after a DMA completion message and the DrivExpress message statistics for the simulation are output.

With that, we come to the end of this tutorial. Please update test\_main.py file and run the simulation again using "*Running The Verilog Simulation*" for reference. If there you made no typos, the error count reported by the DrivExpress message statistics will be zero.

In reality, this kind of script, which waits for the completion of an event does not have to use the event\_callback() command. The code could be simplified to just use the event\_wait() command, but we use both commands on purpose in this tutorial to expose the user to both functions.

One more thing to note: lines 15-17 above would normally be written in a dma\_handler() function, corresponding to an interrupt handler routine. In this case it's not necessary because we're not executing other commands while waiting for the DMA operation to complete.

## 2.5.4 Non-Posted and Posted

Before ending this tutorial, we should further explain the wait\_completion() command which we dared not explain in detail in the main body of the tutorial in section "Access to Configuration Registers". PCI Express configuration read/write and memory read requests are called non-posted requests. A Non-posted request defined as a request that won't return a completion packet across the PCIe link until the operation has actually completed.

At line number 16 of the above code block, the mem\_read() command, which is a non-posted type, issues a memory read request to the DUT and goes to next command without waiting to receive the corresponding completion packet. That means comparison with expected data ext\_buf is not done when the mem\_read() command is initially executed, but rather is delayed until the completion packet is received.

A wait\_completion() command waits for all completion packets to be received for all non-posted commands already executed. But for the code at line number 17, simulation will end before receiving the completion packets for mem\_read() from line number 16. As a result, comparison with ext\_buf will never happen. This is the reason that we use wait\_completion() command at line number 17.

On the other hand, PCI Express memory write requests are called posted requests and no completion packet is returned. Therefore, it makes no sense to use wait\_completion() command for a mem\_write() command.

Please refer to PCI Express specification about non-posted and posted requests for more detail.

**Tip:** Parameter is\_completion\_wait has a similar function. If this parameter is set to True (Default is False), non-posted commands supported by DrivExpress do not proceed to the next command until receiving the completion packet. This is same as executing the wait\_completion() command for every non-posted type command.

The following 2 code examples have the same behavior. It is implied that the instance name of the Root Complex is pcie in the code.

#### Waiting for completion example 1

pcie.cfg\_read16(VENDOR\_ID, 0x1172)

pcie.wait\_completion()

pcie.cfg\_read16(DEVICE\_ID, 0x0004)

pcie.wait\_completion()

#### Waiting for completion example 2

pcie.is\_completion\_wait = True

pcie.cfg\_read16(VENDOR\_ID, 0x1172)

pcie.cfg\_read16(DEVICE\_ID, 0x0004)

## 2.6 About the automatic TCL script

Provided in *\$DRIVEXPRESS\_ROOTDIR/sample/design* there is a TCL script called build\_run.do that automates the following for the ModelSim family of Verilog simulators.

- Generates PCI Express Gen2 x4 sample DMA controller design by using ALTERA Quartus II tool

- Copies DrivExpress license file and sample test script to Verilog simulation directory <sup>2</sup>

- Runs the Verilog simulation

Note:

- 1. License file must be located in *\$DRIVEXPRESS\_ROOTDIR* directory to use build\_run.do file.

- 2. To change PCI Express configuration to Gen2 x8 instead for the sample design, please change the following 2 variables in build\_run.do file.

There are two methods to execute the build\_run.do TCL script. One method executes it from the "Transcript" window after starting the ModelSim Verilog simulator in GUI mode. The other method is executing the vsim command as follows on the command line.

\$ cd \$DRIVEXPRESS\_ROOTDIR/sample/design

\$ vsim < build\_run.do</pre>

The test\_main.py file, which is located in <code>\$DRIVEXPRESS\_ROOTDIR/sample/design/script direc-tory</code>, is executed during Verilog simulation. In the test\_main.py file, test\_pcie\_chain\_dma\_\*.py files are called and executed sequentially.

<sup>&</sup>lt;sup>2</sup> \$DRIVEXPRESS\_ROOTDIR/sample/design/gen2x4/pcie\_proj\_examples/chaining\_dma/drivexpress\_tb

CHAPTER

# **BEST PRACTICES**

In this chapter, explain some basic concepts of DrivExpresswe as well as introduce some techniques for writing test scripts efficiently.

In addition to this, we will cover some higher level concepts like: the relationship between the PCI Express Transaction Layer Packet (hereinafter referred to as TLP) and each DrivExpress command, controlling internal FIFO for TLPs in DrivExpress, and so on.

For FPGA designers and verification engineers who build the test environments, we show how to define DrivExpress as a Verilog module and how the connection between DUT and DrivExpress module should be done.

For each topic we introduce some sample code examples to help with the explanation. If not otherwise specified, we assume that Root Complex class and Simulation Control class have been instantiated using the name pcie and sim respectively.

## 3.1 Python Classes

DrivExpress provides three Python classes, which are the Root Complex class, the Host Memory class, and the Simulation Control class.

Multiple instances of the Root Complex class and the Simulation Control class is prohibited. On the other hand, users can create multiple instances of the Host memory class.

Users can choose an instance name for each class freely; however, it is recommended that easy-to-understand name are used.

As we explained in "Writing A Test Script (Part 1)" of "Tutorial", each class provides some commands and parameters. When writing a command or setting a parameter, the command name and parameter name should be separated with a "." character after the instance name.

Code examples for each class are as follows.

#### Root Complex Class

```

pcie = PcieRootComplex()  # Create PCIe Root Complex instance

pcie.is_32bit_address = True  # 32-bit address mode

pcie.cfg_read16(VENDOR_ID, 0x1172)  # Read Vendor ID, Expected read data is 0x1172

pcie.cfg_write32(BAR0, 0xAAAA0000)  # Set Base Address

pcie.mem_write16(0xAAAA0000, 0xFFF)  # Write 0xFFFF data to 0xAAAA0000 address

```

#### Host Memory Class

```

# Create DMA read buffer memory instance

# Start Address:0x00001000, End Address:0x00001FFF, Initialized by 0x55

dma_rbuf = HostMemory(0x00001000, 0x00001FFF, 0x55) # DMA Read Buffer

# Create DMA write buffer memory instance

# Start Address:0x00002000, End Address:0x00002FFF, Initialized by 0xAA

dma_wbuf = HostMemory(0x00002000, 0x00002FFF, 0xAA) # DMA Write Buffer

# Write 0x11223344 to DMA read buffer offset 0x10 (absolute address 0x00001010)

dma_rbuf.write32(0x10, 0x11223344)

# Read from DMA write buffer offset 0x10 (absolute address 0x00002010)

dma_wbuf.read32(0x10, 0x11223344) # Expacted read data is 0x11223344

```

#### Simulation Control Class

```

sim = SimControl()  # Create simulation control instance

sim.license_file = "/opt/drivexpress/drivexpress_lic_enc.bin"  # Path of license file

sim.msg("Reset DUT")  # Print message

sim.reset(10)  # Assert reset signal during 10 command clock period

```

Please refer to "Class References" about commands and parameters provided by each class for more detail.

## 3.2 Command Queue and Command Type

The commands provided by DrivExpress are categorized into two types. One is a queue-type command which is pushed into the command queue when the built-in Python interpreter interprets it. It is executed after some elapsed time based on the command clock provided in the Verilog testbench. The other is an *immediate* type command, or icommand for short, which is executed instantly when interpreted by built-in Python interpreter. For icommands, the prefix i is put at the beginning of the command name.

## 3.2.1 Simulation Cost

1

Because *i*commands do not consume Verilog simulation time, using *i*commands in your test script will lead increased performance of your Verilog simulation. It is recommended to use *i*commands as often as possible it makes sense, for example during the initialization of host memory.

Let's consider this host memory initialization example.

```

buf = HostMemory(0, 0xFFFF) # Instance of 0x0000000-0x0000FFFF address area

2

# Initializtaion with incremental data by icommand

3

for i in range (0, 0x7FFF):

4

buf.iwrite8(i, (i & 0xFF))

5

6